How to integrate commercial SRAM in my design

Integrating Commercial SRAM in Caravel: A Step-by-Step Guide

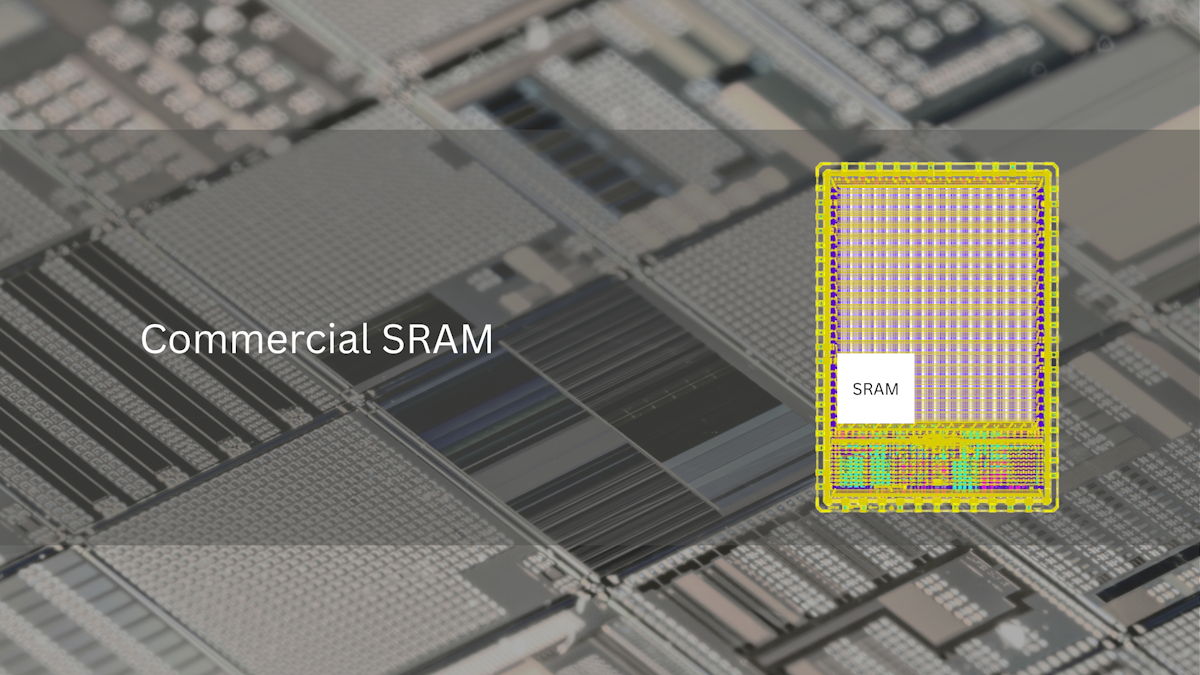

Unlock powerful new capabilities in your Caravel SoC by integrating a high-density, commercially proven SRAM. This production-ready SRAM, already used in billions of chips, can be seamlessly added to your design, enabling everything from high-speed data buffering to complex on-chip computation.

This guide will walk you through the entire process, from installation to final verification.

Prerequisites

Before you begin, please ensure your project environment is fully configured. Follow the ChipFoundry "Start a Project" tutorial to get everything set up and ready for integration.

Step 1: Install the SRAM IP

We'll use IPM, ChipFoundry's IP Manager, to fetch and install the SRAM package directly into your project.

Open your terminal and run the following commands:

# Install the IP Manager

pip install cf-ipm

# Install the 1024x32 SRAM IP

ipm install CF_SRAM_1024x32This will create a new ip/ directory in your project's root, containing all the necessary files for the SRAM macro.

Step 2: Integrate the SRAM in Verilog

Next, you need to instantiate the SRAM within your project. We will replace the default example in the user_project_wrapper with the SRAM's Wishbone-ready wrapper.

- Open the file:

verilog/rtl/user_project_wrapper.v - Replace the existing

mprjinstantiation with the following Verilog code:

/*--------------------------------------*/

/* User project is instantiated here */

/*--------------------------------------*/

CF_SRAM_1024x32_wb_wrapper mprj (

// Power connections

`ifdef USE_POWER_PINS

.VPWR(vccd1), // User area 1 1.8V power

.VGND(vssd1), // User area 1 digital ground

`endif

// Wishbone general signals

.wb_clk_i(wb_clk_i),

.wb_rst_i(wb_rst_i),

// MGMT SoC Wishbone Slave signals

.wbs_cyc_i(wbs_cyc_i),

.wbs_stb_i(wbs_stb_i),

.wbs_we_i(wbs_we_i),

.wbs_sel_i(wbs_sel_i),

.wbs_adr_i(wbs_adr_i),

.wbs_dat_i(wbs_dat_i),

.wbs_ack_o(wbs_ack_o),

.wbs_dat_o(wbs_dat_o)

);What this does: This code instantiates the SRAM and its Wishbone wrapper, automatically connecting it to Caravel's power grid and the primary communication bus. This allows the RISC-V management core to directly access the SRAM.

Step 3: Configure and Harden with OpenLane

This process involves two main stages: first, we harden the SRAM and its Wishbone wrapper into a single macro, and then we integrate that macro into the final user_project_wrapper.

Part A: Harden the SRAM Wishbone Wrapper Macro

The IP you installed includes a Wishbone wrapper around the SRAM core. We need to harden this into its own macro first.

- Get Configuration Files: The necessary OpenLane configuration files for this step are available on GitHub. You can find them here. Place them in the

openlane/directory of your project. - Run Hardening: Execute the following command to start the OpenLane flow for the wrapper:

make CF_SRAM_1024x32_wb_wrapperPart B: Harden the Top-Level User Project Wrapper

Now that our SRAM macro is ready, we need to tell the main user_project_wrapper how to include it.

- Update OpenLane Configuration: Open the file

openlane/user_project_wrapper/config.jsonand update the following variables. - First, define the power connections for the new macro using

FP_PDN_MACRO_HOOKS:

"FP_PDN_MACRO_HOOKS": "mprj vccd1 vssd1 VPWR VGND",Next, tell OpenLane to use the pre-hardened files for the macro by updating the "blackbox" and "extra" file variables:

"VERILOG_FILES_BLACKBOX": [

"dir::../../verilog/gl/CF_SRAM_1024x32_wb_wrapper.v"

],

"EXTRA_LEFS": "dir::../../lef/CF_SRAM_1024x32_wb_wrapper.lef",

"EXTRA_GDS_FILES": "dir::../../gds/CF_SRAM_1024x32_wb_wrapper.gds",

"EXTRA_LIBS": "dir::../../lib/CF_SRAM_1024x32_wb_wrapper.lib",

"EXTRA_SPEFS": [

"CF_SRAM_1024x32_wb_wrapper",

"dir::../../spef/multicorner/CF_SRAM_1024x32_wb_wrapper.min.spef",

"dir::../../spef/multicorner/CF_SRAM_1024x32_wb_wrapper.nom.spef",

"dir::../../spef/multicorner/CF_SRAM_1024x32_wb_wrapper.max.spef"

],- (Optional) Optimize Macro Placement: To improve performance, you can specify the macro's placement to be closer to the Wishbone bus. Edit the file

openlane/user_project_wrapper/macro.cfgwith these coordinates:

mprj 15.06 115 N- Harden the Final Wrapper: Run the make command to generate the final layout for your project:

make user_project_wrapperStep 4: Verify the Integration

Finally, run the included cocotb tests to perform RTL and Gate-Level (GL) simulations, ensuring the SRAM is working correctly. The test files are available on GitHub.

# To run RTL simulation

make cocotb-verify-all-rtl

# To run GL simulation

make cocotb-verify-all-glImportant Note for GL Simulation: Before running the Gate-Level simulation (cocotb-verify-all-gl), you must execute the following workaround script. This script patches the gate-level Verilog file to enable the simulation to run correctly.

python3 verilog/dv/add_ram_workaround.py --gl verilog/gl/CF_SRAM_1024x32_wb_wrapper.vCongratulations! You have successfully integrated a commercial-grade SRAM into your Caravel user project.